DDR學習筆記

摘要的描述相信大家都深有體會,最近鬧得沸沸揚揚的南京貼吧里的《南京珠江路百腦匯就是騙子窩》和網上相關微博《珠江路的騙子,你們還能活多久》等都無情的揭露著電子消費市場的黑暗面,身處其間的我們又該如何練就慧眼,確保自己買到稱心的愛機呢,也許我們可以先從內存說起。

圖 1魚龍混雜的電腦城

1.什么是DDR?

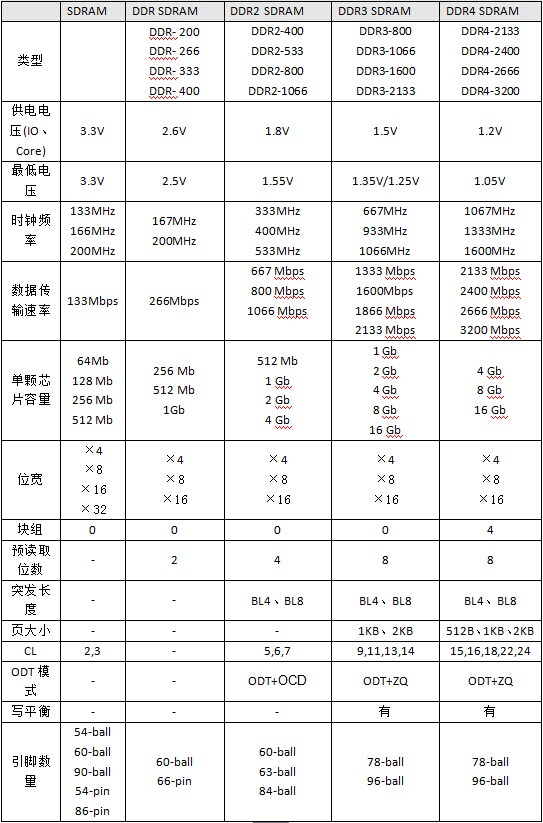

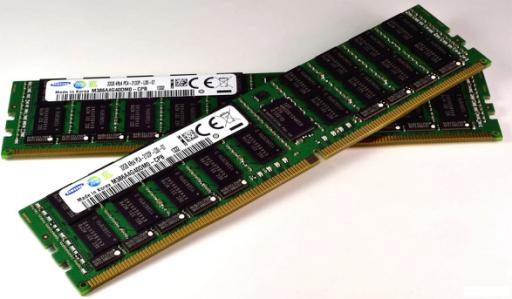

DDR,全稱:DDR SDRAM ,Double Data Rate Synchronous Dynamic Random Access Memary,即,雙數據速率同步動態隨機存取記憶體,也就是我們常用的內存,它從SDRAM的基礎上發展起來,以后依次出現了DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM。它們的能效不斷提升。文章結尾附一張純良心內存能效參數表。

圖 2DDR家族的一員

2.1SDRAM

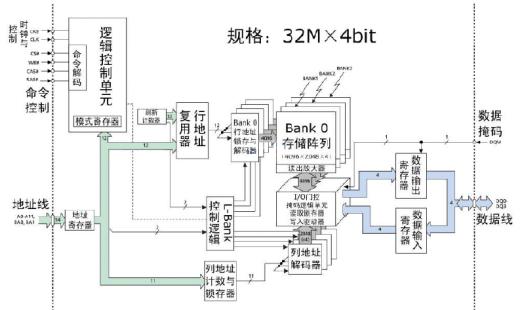

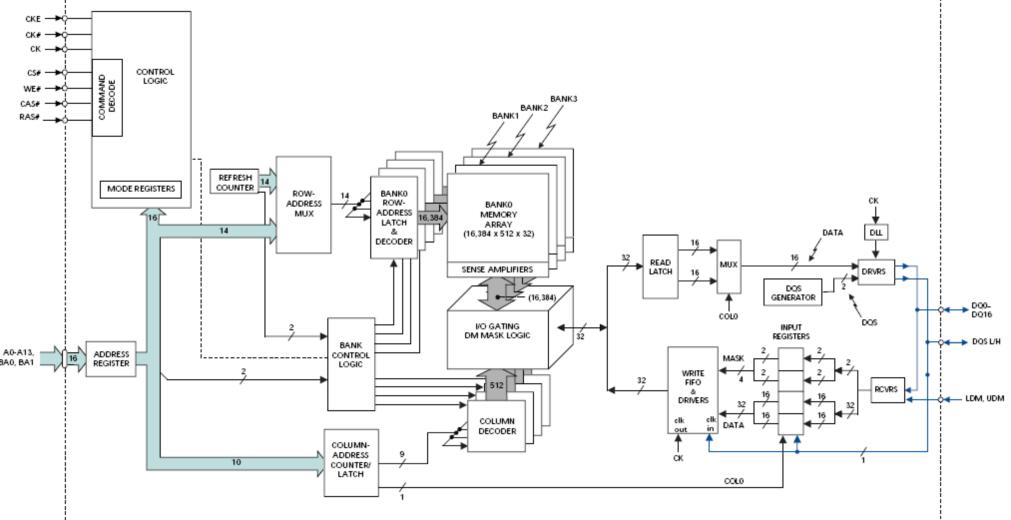

SDRAM內部組成如,可見其組成可以分為幾個部分,存儲陣列、IO門控單元、行列地址解碼器、行列地址鎖存器、邏輯控制單元(包含模式寄存器)、數據輸入輸出寄存器等。

圖 3SDRAM結構圖

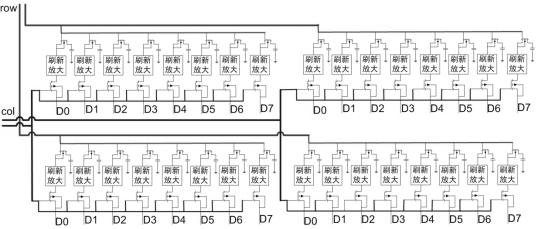

存儲矩陣內部結構,以8位內存單元為例,每個內存單元的數據輸出是并聯在一起,通過行列地址線選中一個存儲單元,

圖 4存儲單元結構圖

存儲容量大小和數據位寬度、行地址、列地址、塊數量等的關系

2.2DDR SDRAM

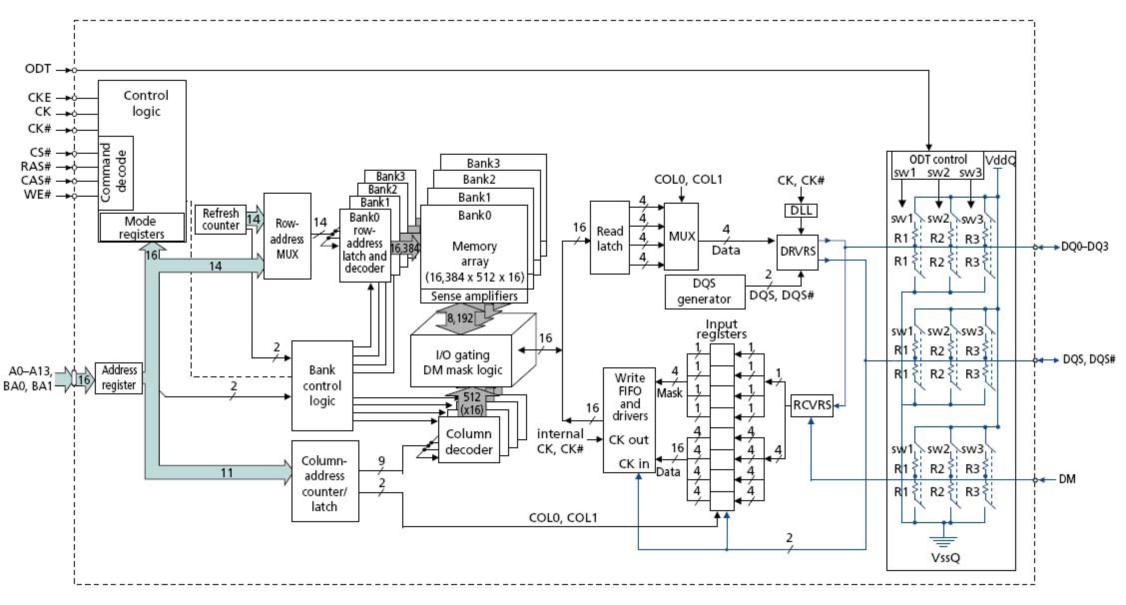

圖 5DDR SDRAM 結構圖

DDR的內部結構與SDRAM相比,數據讀寫部分改進比較大。其一,使用了兩位預讀取的技術;其二,增加了DLL(delay lock loop演示鎖定回路);其三,增加了數據掩碼控制和數據總線反轉控制;此外,時鐘信號和數據選通信號改為差分信號。

2.3DDR2 SDRAM

DDR2 SDRAM整體布局變化不大,在輸入輸出數據總線接口上變化比較多。

圖 6DDR2 SDRAM結構圖

DDR2在DDR的基礎上增加了ODT(on-die termination片上終結,即通過內部邏輯選擇合適的終端電阻進行匹配)功能,預讀取提高到了4位,即每傳輸4個字節/字,只有第一個字節/字有潛伏期。

2.4DDR3 SDRAM

DDR3 SDRAM在輸入輸出數據總線接口上繼續提升性能,在存儲結構上改進工藝,堆疊更多的存儲塊,提高單顆芯片的容量。

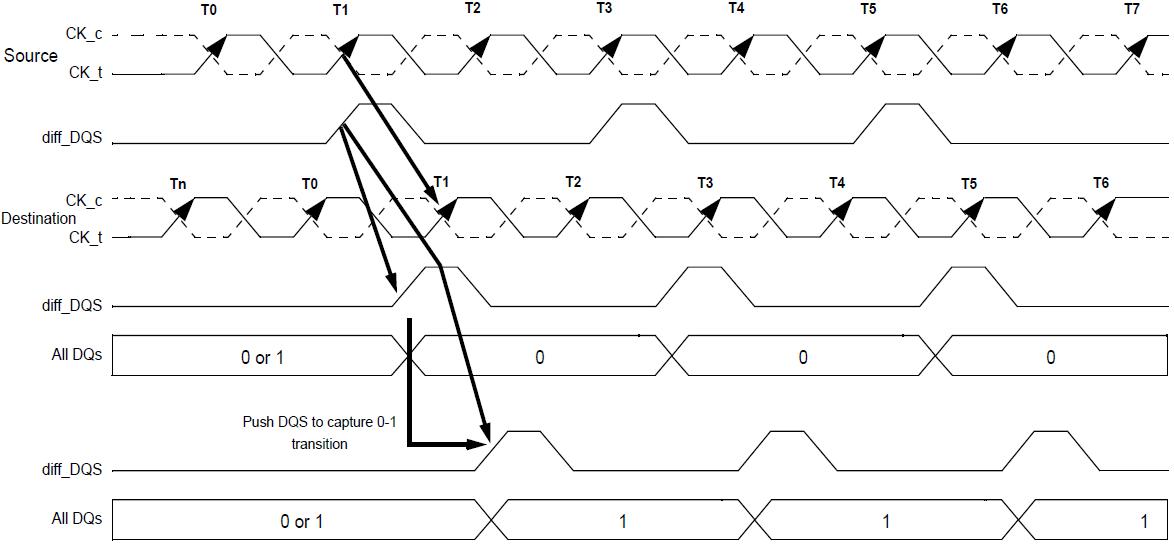

在功能上的改進有,增加了讀寫平衡功能。

圖 7讀寫時序平衡關系

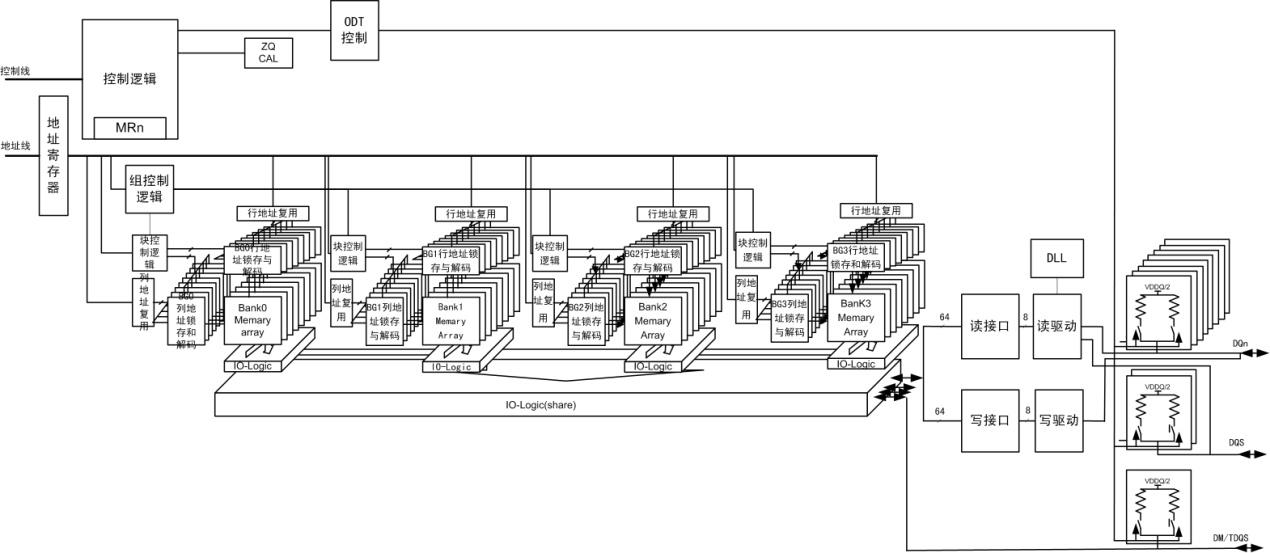

2.5DDR4 SDRAM

DDR4 SDRAM在輸入輸出數據總線接口上繼續改善性能,在存儲結構上繼續改進工藝,不僅堆疊更多的存儲塊,而且使用硅片穿孔工藝把把堆疊成的存儲塊進行并列放置,集中到一顆芯片中,提高單顆芯片的容量。

圖 8DDR4 SDRAM

2.6結尾與附錄

以上便是關于DDR的幾點小知識,站在理論的制高點,結合網上相關防偽攻略,能讓我們更有效的維護自身權益。

篇首說的那張內存參數能效表,請拿好

表 1內存參數表